Paper: Reducing Quantum Error Mitigation Bias Using Verifiable Benchmark Circuits

Joseph Harris · Kevin Lively · Peter K. Schuhmacher

arXiv · 2026

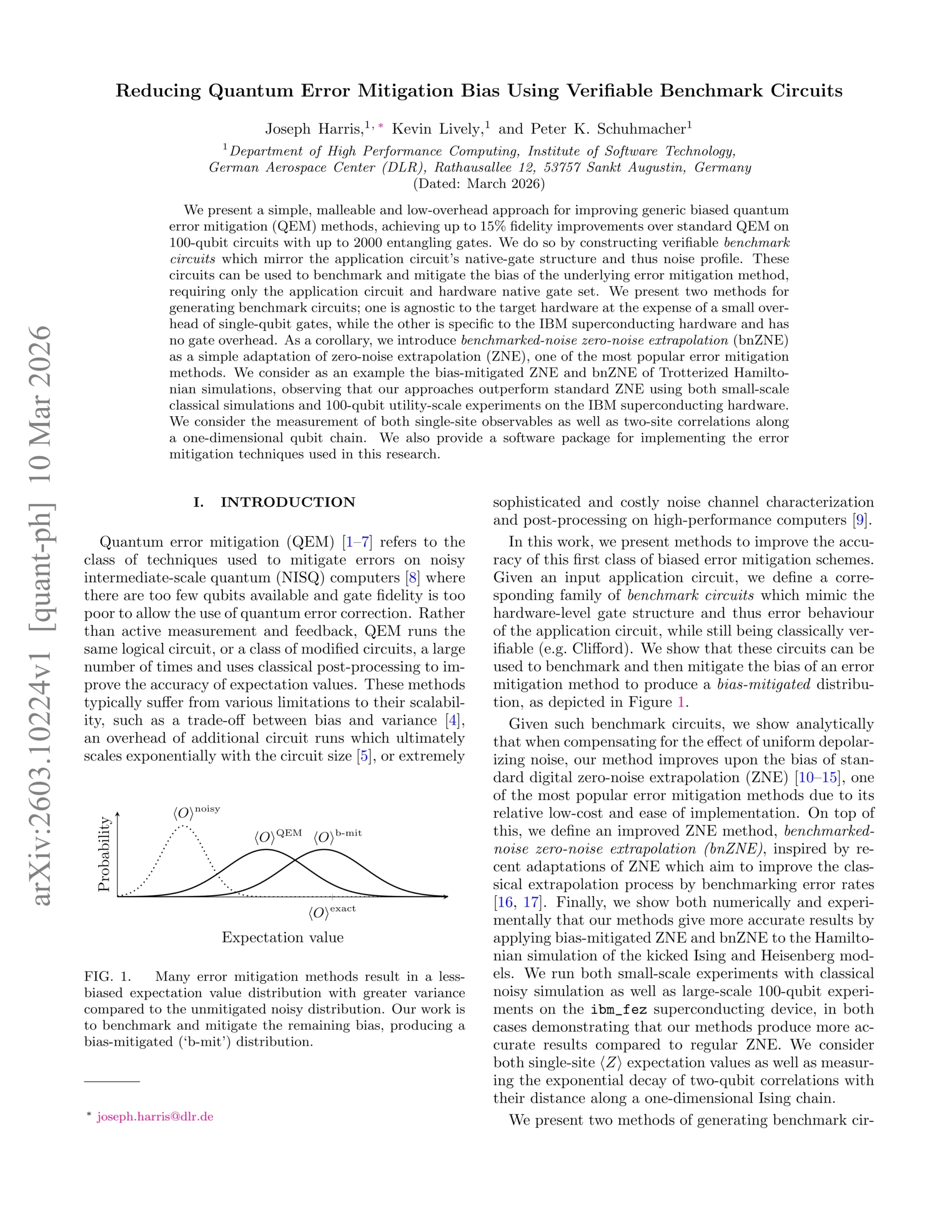

Wir stellen einen einfachen, formbaren und kostengünstigen Ansatz zur Verbesserung generischer vorgespannter Quantenfehlerminderungsmethoden (QEM) vor, der bei 100-Qubit-Schaltungen mit bis zu 2000 Verschränkungsgattern eine Verbesserung der Genauigkeit um bis zu 15 % gegenüber Standard-QEM erreicht. Wir tun dies, indem wir überprüfbare Benchmark-Schaltungen konstruieren, die die Struktur des Anwendungsschaltkreises und damit das Rauschprofil widerspiegeln. Diese Schaltungen können zum Benchmarking und zur Entschärfung der zugrundeliegenden Fehlerminderungsmethode verwendet werden, wobei nur die Anwendungsschaltung und der native Gattersatz der Hardware benötigt werden. Wir stellen zwei Methoden zur Generierung von Benchmark-Schaltungen vor; eine ist unabhängig von der Zielhardware auf Kosten eines kleinen Overheads an Ein-Qubit-Gattern, während die andere spezifisch für die supraleitende IBM-Hardware ist und keinen Gate-Overhead hat. Als logische Folge führen wir die Benchmarked-Noise-Zero-Noise-Extrapolation (bnZNE) als einfache Adaption der Zero-Noise-Extrapolation (ZNE) ein, eine der beliebtesten Methoden zur Fehlerminderung. Wir betrachten als Beispiel die bias-mitigated ZNE und bnZNE von trotterisierten Hamilton-Simulationen und stellen fest, dass unsere Ansätze die Standard-ZNE übertreffen, indem wir sowohl klassische Simulationen in kleinem Maßstab als auch Experimente mit 100 Qubits auf der supraleitenden Hardware von IBM verwenden. Wir stellen auch ein Softwarepaket für die Implementierung der in dieser Forschung verwendeten Fehlerbehebungsmethoden zur Verfügung.

arXiv (2026)

https://doi.org/10.48550/arXiv.2603.10224